丧心病狂!ARM发布CCI-550,最高可支持24核心

英文原文:ARM announces its next-gen CoreLink system for Heterogeneous Computing

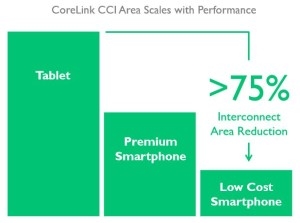

日前,ARM 发布了两套全新的 CoreLink 系统 IP,该技术是专门为下一代移动设备设计的,在性能上有了较大的提升。新的 CoreLink CCI-550 互联总线能够用于 ARM 的 big.LITTLE 多核心架构,能够完美适配拥有“完全一致性”的 GPU,而且延迟更低、吞吐量更高;新的 CoreLink DMC-500 内存控制器,提供了更高的带宽、以及更低的延迟。

新的 Corelink CCI-550 还使最大频宽提升了 60%,并降低了 20% 的延迟。ARM 还指出,由于改良后的互联总线集成了嗅探过滤器,可以节省 100 毫瓦的功耗。CCI-550 还可以配置最高达六个的 CPU 簇(上一代 CCI-500 只支持最高四个 CPU 簇),如果每个簇有四个 CPU 核心,那么整颗处理器就可以做到 24 核心。同时,存储器通道的数量、跟踪器的尺寸、嗅探过滤器的过滤能力也均有一定的提升。该技术在移动和互联网领域有更广泛的适用范围。

这也表明 ARM 公司在异构计算领域已经取得了重大进步。这能够显著提升各部件之间进行通信的带宽限制。更快的互联总线系统也能够使得各个处理器同时处理同样的数据,而无需高速缓存再进行临时存储。这个改良对于如深度智能设备和增强现实设备等的移动领域研发工作来说也意义重大。

“如果想要为客户提供先进的功能,如 4K 视频的录制和播放、120fps 的摄像头、4K 高清显示器等,那么就必定需要将异构的 CPU、GPU 和加速器放在同一个高速缓存系统里同步工作,并且还必须要严格控制好功耗。”

——The Linley Group 高级分析师 Mike Demle

新型的 DMC-500 最高可以支持 LPDDR4-4267 的存储规格,并且带宽提升了 27%,CPU 延迟降低了 25%。如果消费者需要在移动设备上显示更高分辨率的内容,那么增加内存的带宽就显得尤为重要了。

此外,ARM 还透露了即将在其下一代 GPU 上应用的技术。下一代名为“Mimir ”的 Mali GPU 将会是一颗具有“完全一致性”的 GPU,可以提供完全一致的共享虚拟内存,拥有更简单的 OpenCL 2.0/HSA 编程模型,并且将能够完全支持并行加速计算。但是 ARM 并没有再进一步透露关于该技术的更多细节。

这些最新的 ARM 技术预计将会在 2016 年末正式投入市场,所以直到 2017 年之前,作为消费者的我们可能仍然用不上这项技术。

![[HBLOG]公众号](http://www.liuhaihua.cn/img/qrcode_gzh.jpg)